Signal Integrity Considerations for High Speed Digital Hardware Design

Những lưu ý khi thiết kế mạch phần cứng cho tín hiệu tốc độ cao như cách điện, trở kháng, phản hồi, kết nối, đi tín hiệu, nguồn....

Despite the fact that Signal Integrity (SI) is among the most fundamental of design practices for hardware engineers, the digital design community has long ignored it. Through the age of low-speed logic, designing for SI was considered wasted effort, as the probability of SI-related issues was low. However as clock rates and rise times increased through the years, the need for SI analysis and design also increased. Unfortunately many designers have not heeded the call and still neglect to consider SI in their designs.

Modern digital circuits can operate up to gigahertz frequencies with rise times in the order of fifty picoseconds. At these speeds, a carelessly designed PCB trace only needs to be an inch or so long before it radiates. Radiating traces create voltage, timing and interference problems not only on that line, but also across the entire board and even across adjacent boards.

The problem is even more critical with mixed-signal circuits. For example, consider a system that relies upon a high- erformance ADC to digitize received analog signals. The energy on the digital outputs of the ADC could easily be 130dB (10,000,000,000,000 times) more the energy on the analog input. Any noise on the digital side of the ADC could annihilate the low-level analog signal so preventing noise leakage is critical.

Designing for SI need not be an arduous process. The key to designing for SI is to recognise potential problems as early in the design stage and prevent them from causing problems later. This paper outlines some key SI challenges and discusses some steps to address them.

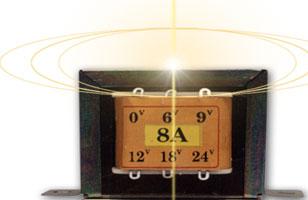

Tính toán quấn máy biến áp 1 pha tần số 50Hz

Tính toán quấn máy biến áp 1 pha tần số 50Hz  Cấu tạo, nguyên tắc hoạt động của Transitor

Cấu tạo, nguyên tắc hoạt động của Transitor  Nguyên lý và sử dụng nguồn xung hay bộ biến đổi nguồn DC-DC

Nguyên lý và sử dụng nguồn xung hay bộ biến đổi nguồn DC-DC  Làm LED trái tim với 8501

Làm LED trái tim với 8501  Ký hiệu, Hình dạng, kiểm tra, Xác định chân Transitor

Ký hiệu, Hình dạng, kiểm tra, Xác định chân Transitor