Ngày 19/05/2022 10:38:56 / Lượt xem: 7022 / Người đăng: biendt

PCB : Kinh nghiệm thiết kế mạch nhiều lớp tốc độ cao

Bài viết được tham khảo nguồn trên Internet tổng hợp lại. Bạn đọc tham khảo để có thêm kinh nghiệm trong thiết kế mạch PCB nhiều lớp tốc độ cao.

1 - Vật liệu làm board

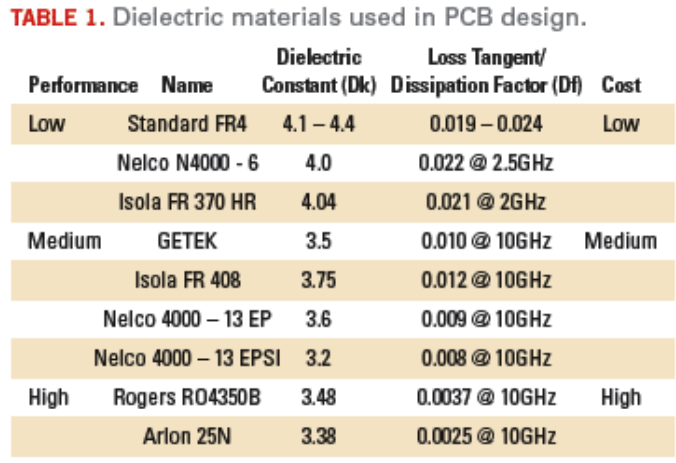

Hầu hết PCB đều được làm từ FR-4, mạch hoạt động tốt với tần số 150Mhz và các đường mạch có độ dài khoảng 8 inch. Bảng sau cho ta một vài gợi ý khi chọn chất liệu làm board.

Dựa vào tần số của board mạch dự định thiết kế, ta có thể chọn chất liệu board tương ứng. Độ suy hao tín hiệu.![]()

Với F là tần số hoạt động của board mạch(Ghz), tan(δ) là hệ số suy hao ứng với mỗi chất liệu, εr là hằng số điện môi của chất liệu.

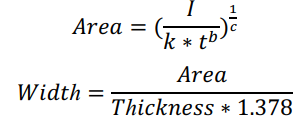

Tính độ rộng đường dây dựa vào cường độ dòng điện: Kích thước dây càng lớn sẽ chịu được dòng tải càng cao. Việc tính độ rộng đường dây còn phụ thuộc vào độ dày lớp đồng và nhiệt độ môi trường xung quanh và nhiệt độ dây trên board. Ngoài ra, độ rộng của đường dây cũng ảnh hưởng đến nhiễu EMI trên board, nhưng không đáng kể. Công thức tính toán kích thước dây khá phức tạp, nên sử dụng một file excel được gắn sẵn các công thức để tính, hoặc có thể tính online trên website: http://circuitcalculator.com/

Khi tính toán trên file excel, đơn vị oz được sử dụng thay mils, 1oz = 1.37mils.

Công thức tính độ rộng đường dây:

Theo qui ước IPC về thiết kế mạch in tốc độ cao, k = 0.015, b = 0.5453, c = 0.7349.

I: Cường độ dòng điện (amps).

t: Nhiệt độ đường dây.

Thickness: độ dày lớp đồng, thường có giá trị từ 0.7 đến 1.4 mils, tùy thiết kế.

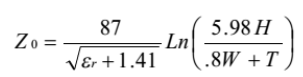

Trở kháng đường dây:

Một tín hiệu điện luôn luôn tồn tại từ trường, cũng đgl tồn tại trở kháng đối với GND. Một đường mạch trên PCB cũng vậy.

Kiểm soát trở kháng đường dây giúp ta có thể đạt hiệu suất hoạt động mong muốn và chống nhiễu giữa các layer.

Để đảm bảo hiệu suất truyền tốt nhất, ta phải đảm bảo các điểm truyền nhận tín hiệu có trở kháng bằng nhau.( Trở kháng phải là một hằng số theo dọc đường mạch. )

Theo IPC, trở kháng ( Zo ) có giá trị từ 25 đến 75 Ohm là lý tưởng cho tín hiệu đơn, với các tín hiệu đi theo cặp thì gấp đôi.

Công thức tính trở kháng đường dây tín hiệu đơn: ( Ohms )

Với: H là bề dày lớp điện môi, W là độ rộng dây, T là bề dày lớp đồng.

Trong thiết kế, hầu như ta chỉ thay đổi 2 thông số là độ rộng đường dây và bề dày lớp điện môi

Nhiễu trên mạch in: Gồm 3 loại chính

Galvanic coupling: Nguyên nhân do tín hiệu có chung đường . Ví dụ như đường GND dẫn đến điện áp rơi trên phần trở kháng chung này.

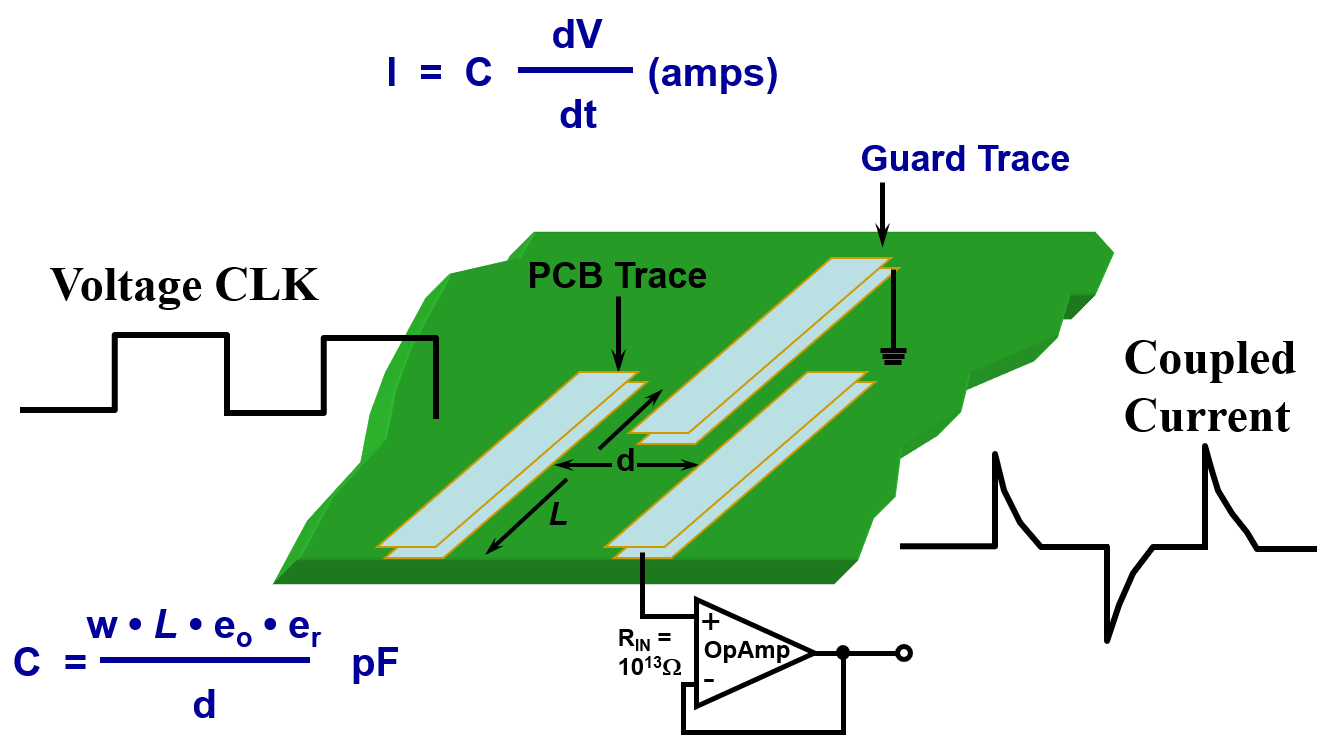

Capacitive coupling: Nguyên nhân là do điện trường giữa đường tín hiệu và đường gây nhiễu, điện trường này có thể được thể hiện qua tụ ký sinh giữa đường tín hiệu và nhiễu.

Inductive coupling: Nguyên nhân là do từ trường giữa đường gây nhiễu và đường tín hiệu. Loại nhiễu này khá phổ biến trong các mạch có tần số cao, hoặc cộng hưởng. Nó có thể được thể hiện qua độ từ cảm giữa 2 đường tín hiệu.

Chống nhiễu trên mạch in là thực hiện giảm thiểu các yếu tố trên, cách sắp xếp linh kiện, đi dây đóng vai trò rất quan trọng. Sau đây là một số tiêu chuẩn đi dây cho việc chống nhiễu.

Giữ khoảng cách giữa các đường tín hiệu bằng 3 lần khoảng cách giữa đường tín hiệu so với GND.

Sử dụng các góc đi dây 45 độ, hoặc đi dây hình vòng cung để tránh sự tích điện tại các điểm nhọn trên dây.

Khi đi các đường tín hiệu, hạn chế việc thay đổi layer. Việc này có thể làm tăng hệ số hỗ cảm. Nếu bắt buộc phải chuyển lớp, thì kích thước via phải là nhỏ nhất.

Đặt tụ điện có điện dung lớn gần nguồn cung cấp , đặt tụ điện có điện dung nhỏ hơn vào gần các linh kiện như IC...Chân nguồn và GND của tụ nên nối trực tiếp vào các plane.

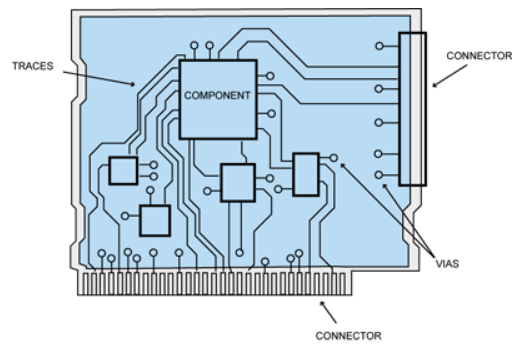

2 - Via

Mỗi via có 1 điện dung so với GND, Công thức :

![]()

Với :

T là bề dày board(inch)

D1 là đường kính lỗ via (inch)

D2 là đường kính Pad đồng (inch)

εr là hằng số điện môi của lớp cách điện

Có 3 loại via cơ bản: Through Via, Blind Via và Bruied Via. Theo công thức trên, kích thước Via của đường dây tỉ lệ thuận với điện dung. Nên khi thiết kế mạch ở tần số cao, các Via nên càng nhỏ càng tốt, nhưng phải đảm bảo chịu được cường độ dòng điện trên đường dây.

Cảm kháng: Khi nối tụ decoupling vào Ground Plane, ta cần quan tâm đến hệ số tự cảm của via.

![]()

Với L là điện cảm via (nH), h là chiều dài via (inch), d là đường kính via (inch).

Theo công thức trên, sự thay đổi đường kính via gây ảnh hưởng rất nhỏ đến L. Tuy nhiên, L sẽ thay đổi một số khá lớn khi h gia tăng hoặc sử dụng nhiều via song song. Do đó, để nối các tụ decoupling với lớp GND, hãy sử dụng 2 via cho mỗi chân linh kiện. Để giảm nhỏ điện cảm, ta cần sử dụng nhiều via phân bố trên từng khoảng đều đặn xuyên suốt board.

Return Path: Một đường tín hiệu, nếu chuyển layer bằng cách đi qua các lớp plane, sẽ làm Return Path trở nên phức tạp. Nếu board có 2 lớp plane, hãy đặt thêm 1 via GND → GND gần via tín hiệu để đảm bảo Return path liên tục.

Tụ decoupling: Cấp đủ nguồn để IC hoạt động, ngăn tín hiệu tần số cao chạy khắp board. Tụ decoupling nên được bố trí xuyên suốt trên board. Tính số layer: Đối với các loại mạch in tốc độ cao, cần chống nhiễu tốt hơn nên cần board ít nhất 4 lớp trở lên.

Capacitor chia thành 2 loại:

+ Decoupling capacitor ( tụ Bypass ) : Là những tụ có điện dung nhỏ (thường từ 0.1 uF trở xuống), đặt gần tải càng tốt, gần chân IC...

Mục đích: Làm suy giảm biên độ thành phần AC,do vậy các thành phần dao động sẽ đi qua tụ và xả xuống GND.

Bù điện áp bị mất do dòng rò Icc theo đáp ứng các kích thích ở ngõ ra.

Các tụ có điện dung nhỏ (0.001uF ) sẽ chịu loại đi những ripple (dao động gợn) có tần số cao, tụ trung bình(0.1uF) loại đi các ripple trung tần và các tụ lớn (4.7-47uF) để loại đi các tần số thấp hơn.

+ Bulk capacitor ( tụ lọc ) : Là những tụ có điện dung lớn (phân cực, không phân cực), thường đặt gần nguồn.

Sử dụng Ferrite Beads để cách ly nhiễu đầu vào, không nhạy cảm từ trường bên ngoài phụ thuộc nhiệt độ làm mất từ trường, điểm Curie là phụ thuộc vật chất từ 120 ° C đến 500 ° C. Khi lựa chọn Ferrite Beads luôn biết tần số nhiễu không mong muốn.

- Resistor Pullup-Pulldown : là điện trở có tác dụng ghim mức điện áp, giá trị khoảng 4.7K, 10K. Cố gắng đặt gần ngõ vào/ra càng tốt.

+ Pull up: Ghim mức 1, 1 đầu kéo lên VCC.

+ Pull down: Ghim mức 0, 1 đầu kéo xuống GND.

Đối với PCB, các lớp (layer) dc chia làm 2 loại: Dẫn điện và Không dẫn điện:

+ Dẫn điện (Conductor Layer): là những lớp có đồng (đường mạch, mảng đồng). Ví dụ như Top, Bottom, Inner (GND Plane, Power Plane, Signal).

+ Không dẫn điện (In-conductor Layer): Là những lớp không liên quan đến điện: Silkscreen (tên, đường viền của linh kiện, hay những ghi chú....). Solder Mask là lớp bảo vệ mạch khỏi môi trường bên ngoài. Assembly là lớp để tráng chì hàn lên chân linh kiện (thường dùng cho lắp ráp tự động, đôi khi in ra file để tham khảo vị trí linh kiện ).

Vậy thôi, còn các layer khác tùy thuộc vào phần mềm mà sẽ gán những thuộc tính vào.

Chú ý: Thí dụ mình nói PCB 10 layers, tức là có 10 lớp dẫn điện nhé (ko bao gồm lớp không dẫn điện).

Differential pair thực ra chỉ là một tín hiệu, nhưng người ta chia thành Negative và Positive để lấy Vi sai 2 tín hiệu nhằm mục đích chống nhiễu trong tần số cao. 2 sợi này cố gắng chạy song song với nhau nhiều nhất có thể, chênh lệch chiều dài thường là +/- 5 mils (thông thường).

Về bề dày, khoảng cách của đường mạch, tùy thuộc vào thông số Impedance, vật liệu, vẽ ở lớp nào mà ta sẽ tính toán cụ thể (như mình đã chia sẻ phần đầu). Có thể tham khảo ở đây: Differential signaling - Wikipedia, the free encyclopedia

Các chuẩn DDR2, DDR3, PCI, USB, I2C,..thì tài liệu rất nhiều trên mạng. Điều quan trọng là phải nắm rõ cơ bản trước. Ví dụ DDR2/3 thì mỗi khách hàng sẽ có 1 guideline riêng chi tiết, nhưng chỉ xoay quanh các vấn đề sau:

+ 1 Byte (8 Bits) Data/Address phải đi trên 1 layer cùng với bit Stroke. Cũng có khách hàng muốn vẽ 2,3,4 byte trên 1 layer.

+ Kiểm soát chiều dài đường mạch.

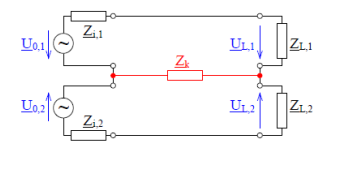

1. Galvanic coupling: Nguyên nhân do tín hiệu có chung đường (ví dụ như đường GND) dẫn đến điện áp rơi trên phần trở kháng chung này. Mô hình của nó có thể được hình dung qua model sau:

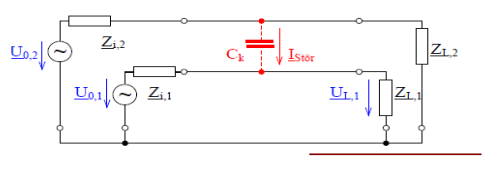

2. Capacitive coupling: Nguyên nhân là do điện trường giữa đường tín hiệu và đường gây nhiễu, điện trường này có thể được thể hiện qua tụ ký sinh giữa đường tín hiệu và nhiễu. Mô hình của nó được hình dung qua hình sau:

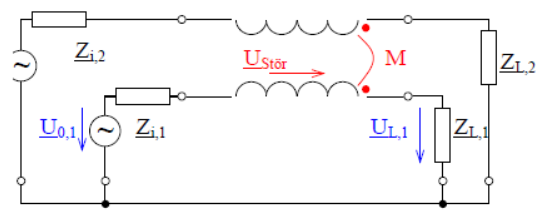

3. Inductive coupling: Nguyên nhân là do từ trường giữa đường gây nhiễu và đường tín hiệu. Loại nhiễu này khá phổ biến trong các mạch có tần số cao, hoặccộng hưởng. Nó có thể được thể hiện qua độ từ cảm giữa 2 đường tín hiệu. Model:

1. Bề rộng đường mạch (Trace Width, mình gọi tắt là TW) KHÔNG ảnh hưởng NHIỀU đến việc chống nhiễu, một số ý kiến cho rằng TW nhỏ sẽ nhiễu hơn chút xíu so với TW lớn (theo tính toán/mô phỏng của họ) nhưng KHÔNG ĐÁNG KỂ.

Tuy nhiên, theo công thức tính toán Cross Talk Noise (Nhiễu giữa các tín hiệu) thì không đề cập đến TW, mà chỉ đề cập đến Khoảng Cách giữa các đường mạch và Bề dày lớp cách điện giữa Lớp Tín Hiệu và Return Path Referrence (GND).

Crosstalk ~ K / (1 + (D/H)*(D/H)), where D: distance between two traces = center to center. H: height above the reference plane PCB Calculator

Khoảng cách an toàn giữa các tín hiệu: Nếu đường mạch là 10 mils thì khoảng cách tối thiểu giữa 2 đường (cạnh tới cạch) là 3x TW = 30 mils, lí tưởng là 50 mils.

2. Bạn có thắc mắc là thấy một số PCBs, đường mạch chỉ 6-8 mils. Không phải một số, mà là HẦU HẾT các Single End signals (tín hiệu đơn) chỉ sử dụng TW ~ 6-10 mils. TW = 10 mils (1 Oz Copper) là có thể chịu dc dòng 1 A tại nhiệt độ 20'C rồi .

Như vậy, nếu đường mạch to/rộng thì khoảng cách giữa 2 tín hiệu phải tăng, ít không gian để chạy, số tín hiệu chạy trên 1 lớp bị hạn chế,...

3. Mình xin nói thêm các yếu tố cơ bản mà mình biết chống nhiễu trong PCB.

+ Tần số tín hiệu hoạt động: Cái này quyết định Vật Liệu làm PCB, Mỗi loại vật liệu sẽ tương ưng với khoảng tần số riêng và đương nhiên giá cả cũng rất khác.

+ Dạng thiết kế (RF, High Speed, Analog, Digital,...). Với mỗi dạng thì sẽ có những yêu cầu cụ thể riêng biệt. Ví dụ: Bạn thiết kế Mạch RF mà không có GND Fence Via/Plane chạy cùng với tín hiệu RF thì hỏng toàn bộ.

+ Impedance: (Trở kháng Z). Hầu hết PCB đều yêu cầu kiểm soát trở kháng (Impedance Control) để đạt dc hiệu suất cao nhất.

Các bạn tham khảo định lí :Maximum power transfer theorem - Wikipedia, the free encyclopedia

Để đạt dc công suất lớn nhất thì trờ kháng Ngõ Vào phải BẰNG Ngõ Ra. Hãy tưởng tượng PCB (gồm cả linh kiện) cũng là 1 Device (thiết bị) cũng có INPUT và OUTPUT.

Trong giới hạn bài viết này mình chỉ nói đến Kiểm Soát Trở Kháng của Bare PCB (chưa Asembly), không nói đến trở kháng của linh kiện (Tụ, Trở, Cuộn, IC,..) vì cái này dính đến Lí Thuyết Mạch.

+ Impedance: (Trở kháng Z). Chú ý: PCB Bắt Buộc phải từ 2 layers/lớp trở lên (Multi-layer), và Layer GND Bắt Buộc phải nằm kề Layer Signal/tín hiệu. Trước đây khi còn là SV, mình nghe nói đổ đồng để chống nhiễu, nhưng nó chỉ chống nhiễu trên Layer/Lớp đó thôi, còn giữa 2 lớp tín hiệu thì phải chèn 1 lớp GND vào giữa để chống nhiễu, đồng thời kiểm soát trở kháng (Impedance

Control).

Vậy Z = ?. Theo lí thuyết thì Z = 25 ~ 75 ohms, nhưng thực nghiệm cho thấy, tại 75 Ohm thì đạt hiệu suất cực đại nhưng xuất hiện dòng điện rò (leakage current), người ta thấy rằng Z ~ 53.3 Ohm là lí tưởng. Từ đây người ta làm tròn thành 50 Ohm cho dễ. Bên Viễn Thông thì thường Z = 75 Ohm. Mình đang nói Single End Signal, nếu Diferential Pairs thì gấp đôi ~ 100 Ohm.

-Công thức: Search "Impedance Calculator/Formula" là ra công thức (mình ko nhớ công thức vì xài phần mềm quen rồi, các bạn cũng có thề dùng phần mềm miễn phí Impedance Calculator của Polar Intrusment, hay tại đây cũng dc :PCB Calculator.

-Các yếu tố ảnh hưởng đến Z (Single End Signal-Tín hiệu đơn hay 1 Net thông thường:

Trace Width: Bề rộng. TW càng nhỏ thì Z càng lớn (6~10 mils là nhỏ rồi).

.Trace Thickness: Bề dày. TT càng nhỏ thì Z càng lớn (Thường thì TT = 1 Oz ~ 1.4 mils)

.Dielectric Thickness: Bề dày lớp cách điện (Prepreg hay Core). DT càng nhỏ thì Z càng nhỏ. Min DT = 3 mils.

.Dielectric Constant: Hằng số điện môi e (phụ thuộc vào vật liệu cấu thành PCB). e càng nhỏ thì Z càng lớn.

Hầu như ta chỉ thay đổi 2 thông số: "Trace Width: Bề rộng" và "Dielectric Thickness: Bề dày lớp cách điện". Khi tăng DT thì Z tăng, nhưng lại có thể vi phạm đến tổng số lớp trên 1 bề dày PCB cho trước. (Ví Dụ: Bề dày PCB là 100 mils, thì tổng số Lớp có thể là 17 Layers, khi tăng DT (để đạt Z) thì Maximum Layers sẽ bị giảm).

Do đó giảm "Trace Width: Bề rộng" là ảnh hưởng mạnh nhất đến trở kháng.

Tóm Lại:

- Trở Kháng Z: Để đạt hiệu suất mong muốn + Chống nhiễu giữa các Layer/Lớp.

- "Trace Width: Bề rộng": Càng nhỏ --> Z càng lớn (là điều mong muốn).

Bạn Tiger: Độ ổn định của mạch phụ thuộc vào nhiều yếu tố, bề rộng mạch cũng có thể gọi là 1 trong những yếu tố đó (TW nhỏ: Dễ kiểm soát Z, Khoảng cách 2 tín hiệu càng rộng, số Layers giảm,..).

Ngoài ra còn nhiều yếu tố khác như Component Placement (đặt linh kiện), Equal Length (cùng chiều dài mach), Splitting Power (Đổ đồng cho Nguồn), Thermal (Nhiệt),…

(Bài viết sưu tầm kinh nghiệm của thành viên trên mạng chia sẻ)

Tính toán quấn máy biến áp 1 pha tần số 50Hz

Tính toán quấn máy biến áp 1 pha tần số 50Hz  Cấu tạo, nguyên tắc hoạt động của Transitor

Cấu tạo, nguyên tắc hoạt động của Transitor  Nguyên lý và sử dụng nguồn xung hay bộ biến đổi nguồn DC-DC

Nguyên lý và sử dụng nguồn xung hay bộ biến đổi nguồn DC-DC  Làm LED trái tim với 8501

Làm LED trái tim với 8501  Ký hiệu, Hình dạng, kiểm tra, Xác định chân Transitor

Ký hiệu, Hình dạng, kiểm tra, Xác định chân Transitor